- A+

芯片企业经营(IDM、Fabless、Foundry)三种模式

芯片产业链主要包含集成电路设计、晶圆制造、封装测试等环节,按照企业经营参与其中环节划分为三种经营模式。

一、IDM(Integrated Device Manufacture:集成器件制造)模式

企业拥有自己的圆晶、封装厂和测试厂,自行完成芯片的全生命周期,包括从设计到制造的整个过程。这种模式允许企业更好地控制产品质量和技术创新,同时降低成本和提高生产效率。然而,IDM模式需要大量的初始投资和维护成本,适用于技术密集型和资金密集型的行业。采用IDM模式的企业通常是技术领先的全球性大公司,如三星、德州仪器(TI)、英特尔等。

二、Fabless(无晶圆厂)模式

没有自己的生产制造晶圆工厂,公司主要负责集成电路的设计、(销售前的)测试和销售,而将晶圆制造、封装、测试等生产环节外包给专业的代工合作伙伴来完成。Fabless模式的企业专注于设计技术和知识产权的创造,从而可以更专注于提高设计能力和产品性能,同时减少设备和固定成本,降低技术风险,并利用全球范围内的优质资源。然而,这种模式也意味着企业需要依赖代工合作伙伴的产能。Fabless模式的企业如苹果、海思

三、Foundry(制造厂、代工厂)模式

只负责制造、封装、测试等其中一个环节,不负责芯片设计,可以同时为多家设计公司提供服务,Foundry(代工厂)模式企业没有设计、销售等环节的风险,但需要持续投资从事的环节,以保持先进的工艺。

1、CP测试:

CP测试,英文全称Circuit Probing、Chip Probing,也称为晶圆测试,测试对象是针对整片wafer中的每一个Die,目的是确保整片wafer中的每一个Die都能基本满足器件的特征或者设计规格书,通常包括电压、电流、时序和功能的验证。可以用来检测fab厂制造的工艺水平。

CP的难点是如何在最短的时间内挑出坏的die,修补die。

常用到的设备有测试机(IC Tester)、探针台(Prober)以及测试机与探针卡之间的接口(Mechanical Interface)

2、FT测试:

FT测试,英文全称Final Test,是芯片出厂前的最后一道拦截。测试对象是针对封装好的chip,CP测试之后会进行封装,封装之后进行FT测试。可以用来检测封装厂的工艺水平。

FT测试一般分为两个步骤:1)自动测试设备(ATE)2)系统级别测试(SLT)---2是必须项,1一般小公司可能用不起。ATE测试一般只需要几秒钟;SLT一般需要几个小时,逻辑比较简单。

FT的难点是如何在最短的时间内保证出厂的Unit能够完成全部的功能。FT需要tester(ATE)+ handler + socket

罗德与施瓦茨(中国)科技有限公司https://www.rohde-schwarz.com.cn

罗德与施瓦茨两人师从Esau教授,并于1931年自耶拿大学物理技术学院获得博士学位,由于对射频测量的极大兴趣,两人毕业后仍保持联系。 在正常工作之外,两位物理学家还不断地进行气体放电特性的实验,并于1932年共同研制出他们第一台测量仪器,波长从6至3600米的精度频率计。 首次通过一种新开发的用于射频的介电质材料进行了精确的测量。1933年罗德与施瓦茨公司(R&S公司)正式成立,总部位于德国,现在美国、中国、日本、新加坡、巴西和阿布扎比(阿联酋)都设有地区支持中心,业务遍及全球70多个国家。

什么是保密协议(NDA)

保密协议(NDA)是一份具有法律约束力的合同,旨在建立双方或多方之间的保密关系。签署该协议的各方承诺不会向未被协议涵盖的任何第三方透露所共享的敏感信息。客户与恩智浦进行任何保密信息交流时均需签订保密协议。

谁需要签署保密协议?

从他方接收专有或保密信息的个人,以及向他方提供此类信息的个人,都有责任保护这些信息。专有或保密信息,无论是有形信息还是无形信息,只要涉及从恩智浦外部接收或提供给外部的情况,就必须制定相应的保密条款和条件。

保密协议的作用是什么?

保密协议:要求接收方保护披露方的保密信息,不得泄露给第三方;确定披露和使用保密信息的条款和限制;仅允许基于“需要知道”的原则在接收方内部披露保密信息,帮助实现保密协议所述的授权目的。

半导体、IC 设计是什么?

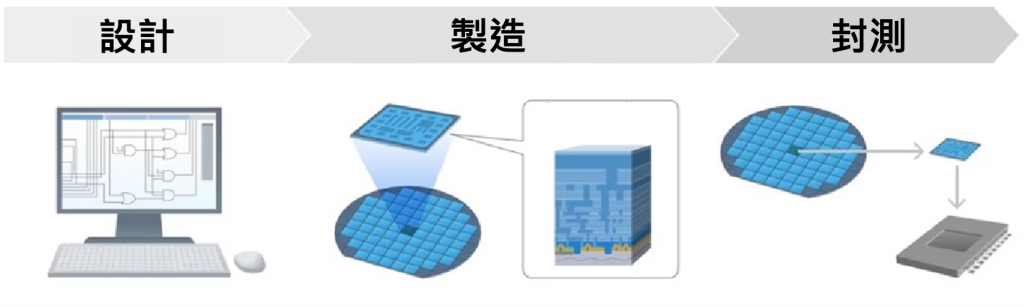

半导体是一种材料的总称,其特色在于导电能力介于导电与绝缘体间。 最为常见、应用最为普及的是萃取自沙子中的元素硅(Silicon, Si)为材料的半导体。 晶圆(Wafer)是将元素硅经过一连串的加工后所形成可以放置电子元件的一片片晶圆。 晶片(Chip),则是晶圆依照电路设计图安装完后,进行切割、封装的成果,芯片的正式名称为「集成电路」Integrated Circuit 简称IC 。 一个芯片IC从无到有可以大致分为设计、制造、封测三阶段,对应大致流程半导体产业的上、中、下游。

半导体产业上游

IC 设计

制造任何产品之前都需要设计图,制造IC芯片也不例外。 IC 设计公司「Design House」的工作就是将客户或自行开发产品的规格与功能,设计芯片上的功能、程式码、组件以及组件之间的电路,所产出电路设计图,也因此 IC 设计公司不会建立自己的工厂制造芯片,故也称为无厂半导体公司「Fabless」。

此外,IC芯片在设计上相当复杂且费工,为增加效率,IC 设计公司便向IP 公司购买IP 模组,来完成芯片上的某些特定功能。 IP 又称作硅智财,即IC 设计中的知识产权,IP 公司便是提供芯片设计的可重用模组,以减少IC 芯片设计周期。

半导体产业炼中游

IC 制造

当IC设计公司将电路图设计出来后,便可以进入制造阶段。 IC 制造就是将设计好的电路图通过光学成像的原理转移到硅晶圆之上。 小小的晶圆上蕴含着相当精密的程序与工法,利用光罩印上电路基本图样,再以特殊工法(氧化、扩散、CVD、蚀刻、离子植入等方法),将电路及电路上的组件,于晶圆上制作出来。 且因电路设计属于层状结构,因此需要经过多次的光罩投入、图形制作、形成线路与组件等重复程序,才能制作出完整的集成电路。

整个IC制程中,运用到非常多的技术,这些技术需要很特定的设备,以及重要的材料,像是硅晶圆、转印电路图所使用的光罩、蚀刻与光阻时所需要的化学品等,也都属于半导体产业中游的一环。

半导体产业链下游

IC 封装、IC 测试

经过层层关卡制造后,晶圆会被送至封装厂,进行IC封装与测试。 IC 封装是将加工完成后的晶圆,切割过后的晶粒,以塑料、陶瓷或金属包覆,保护晶粒以免受污染且易于装配,并达成芯片与电子系统的电性连接与散热效果。 IC 测试则可分为两个阶段,第一个阶段是进入封装之前的晶圆测试,主要测试电性; 第二个阶段则是IC成品测试,主要在测试IC功能、电性与散热是否正常,以确保品质。

半导体产业垂直整合

集成组件制造厂( Integrated device manufacturer, IDM)

IDM 厂就是一家公司完全覆盖从芯片设计、制造、封装和测试等多个产业链环节。 早期的半导体公司多半为IDM厂商,但随着IC芯片的设计和制作越来越复杂,难度与费用也越来越高。 因此1980年代末期,半导体产业逐渐转向专业分工模式,有些公司专门做设计,然后交由其他公司制造和封装测试。